PlanAhead系统教程

PlanAhead 提供了一个 RTL 到比特流设计流程,具有新的改进用户界面和项目管理功能。借助于 PlanAhead 软件,您可以通过查看实现和时序结果轻松地分析关键逻辑,并且利用布局规划、约束修改和多种实现工具选项进行有针对性的决策,从而提升设计性能。它具有大量的设计探索与分析特性,能够帮助您在 RTL 编码和综合与实现之间的进行折中。 通过整合 ISE 项目浏览器(Project Navigator)而变得方便使用,PlanAhead 软件扩展了逻辑设计流程方法,能够帮助您通过布局规划、多个实现进程、层次化探索、快速时序分析和基于模块的实现来发挥设计的最大优势。

首颗28nm FPGA实测 包含10Gbps眼图

The first-ever 28nm FPGA demonstrates major design functionality within 48 hours, including 10Gbps eye quality.

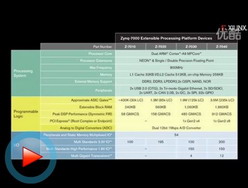

Xilinx ARM高管联合介绍可扩展Zynq处理平台

Vidya Rajagopalan, VP of Processing Platforms at Xilinx, and Dipesh Patel, VP of Technology, Physical IP Division at ARM, introduce the Zynq-7000 Extensible Processing Platform from Xilinx. This new class of product combines an industry-standard ARM® dual-core Cortex™-A9 MPCore™ processing system with Xilinx unified 28nm architecture.

赛灵思展示28Gbps高速串行收发器性能

集成了 28Gbps 收发器的 Xilinx Virtex®-7 HT FPGA 可实现业界最高带宽的平台。这些器件可为 100G-400G 线路卡乃至更先进的新一代通信系统提供最大的单 FPGA 解决方案。