【上海线下】开始报名!RF 设计与仿真方案研讨会 — 2024 Cadence 中国技术巡回研讨会

随着 5G/6G 和毫米波技术的不断演进,传统的射频(RF)设计和分析方法面临着越来越难以克服的挑战。从 III-V MMIC 到 mmWave IC 芯片,到封装和 PCB,每个组件和系统集成的交互比过去任何时候都多。组件协同设计和全系统电磁场仿真,已经是确保电路功能和系统可靠性的强制要求。为了应对这些挑战,您需要涵盖 IC,封装和 PCB 的全流程工具和全新的设计方法学,进行集成化的设计和全系统分析。融合人工智能(AI)的 EDA 工具链,以其自动化的设计流程和高效的优化技术,可以帮助 RF 工程师实现最优的设计,避免无效的设计迭代。

本次 RF 设计与仿真方案研讨会 将重点介绍 Cadence 的跨平台RF设计仿真技术,包括 Virtuoso RF 设计平台,AWR/Allegro RF PCB 设计平台,高效的 SpectreRF 电路仿真引擎,黄金标准的 EMX/Clarity 全波电磁场仿真引擎,以及基于 AI 技术的 Optimality 全局优化引擎。

Cadence 诚挚邀请 RFIC 设计工程师,毫米波/相控阵天线设计工程师,微波电路设计与验证工程师,数模混合电路设计工程师,射频 PCB 设计工程师,测试人员,射频仿真工程师等参加 4 月 18 日在上海举办的“RF 设计与仿真方案研讨会” ,共同探讨从 IC 到 PCB 级跨平台的一体化设计与分析方法,并与现场来自高校的射频设计仿真专家交流。

会议日期&地址

会议注册

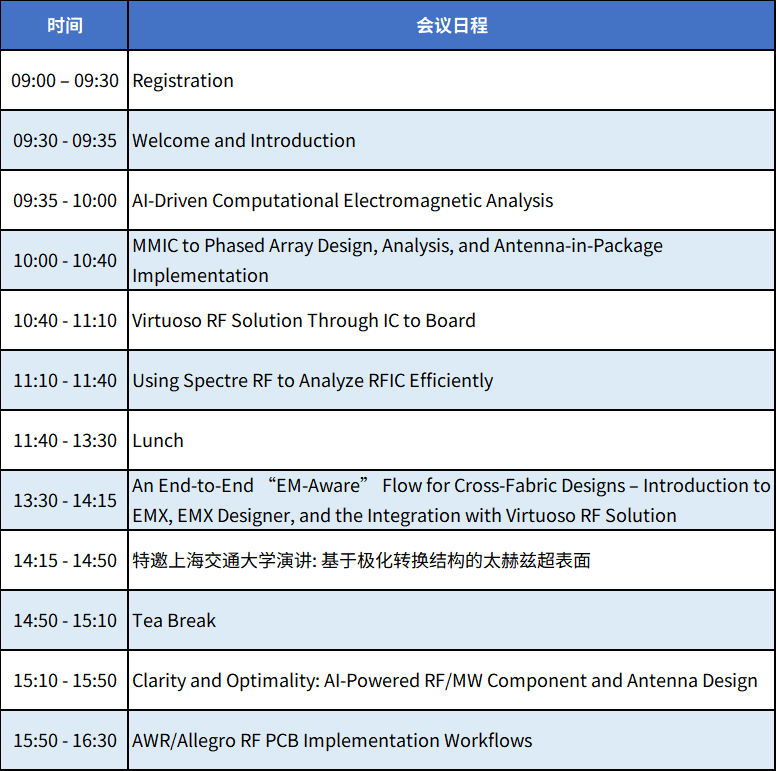

会议日程

(*请注意,会议日程可能根据实际情况进行调整)

上下滑动 查看完整主题演讲简介

Cadence 期待您的报名和参与!

关于 Cadence

Cadence 是电子系统设计领域的关键领导者,拥有超过 30 年的计算软件专业积累。基于公司的智能系统设计战略,Cadence 致力于提供软件、硬件和 IP 产品,助力电子设计概念成为现实。Cadence 的客户遍布全球,皆为最具创新能力的企业,他们向超大规模计算、5G 通讯、汽车、移动设备、航空、消费电子、工业和医疗等最具活力的应用市场交付从芯片、电路板到完整系统的卓越电子产品。Cadence 已连续九年名列美国财富杂志评选的 100 家最适合工作的公司。如需了解更多信息,请访问公司网站 www.cadence.com。

© 2024 Cadence Design Systems, Inc. 版权所有。在全球范围保留所有权利。Cadence、Cadence 徽标和 www.cadence.com/go/trademarks 中列出的其他 Cadence 标志均为 Cadence Design Systems, Inc. 的商标或注册商标。所有其他标识均为其各自所有者的资产。

京公网安备 11010802033920号

京公网安备 11010802033920号