Cadence 在 2024 Chiplet 峰会上树立了 UCIe 互联的最高标准

本文翻译转载于:Cadence blog

Cadence 在 2024 Chiplet 峰会期间展示了用于芯片间互联的多个 IP。与会者与我们讨论了他们的小芯片和多芯片设计需求,并了解了 Cadence IP 如何支持他们以最佳 PPA 目标实现系统需求。 Cadence UCIe ™ IP 硅演示因其广泛的测试而引起轰动。

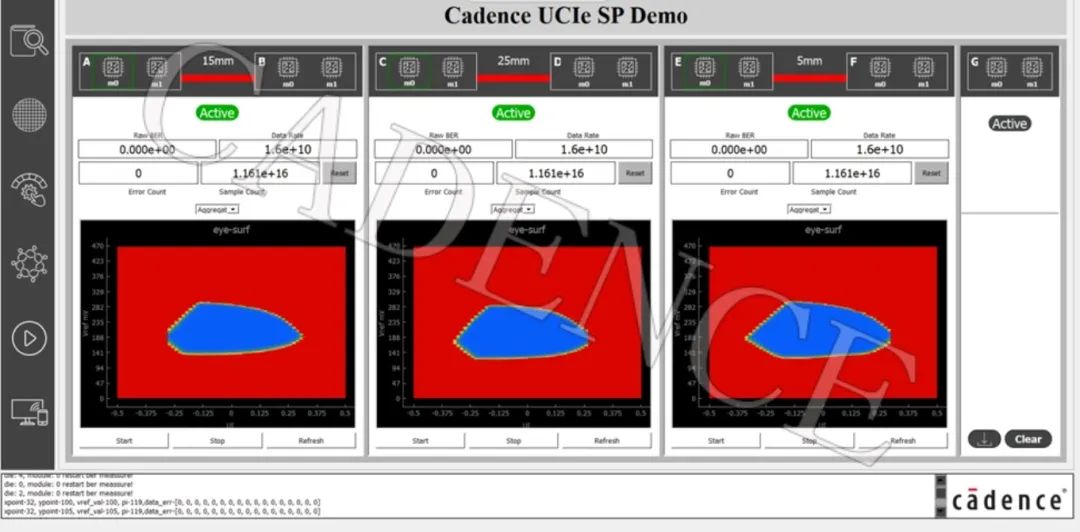

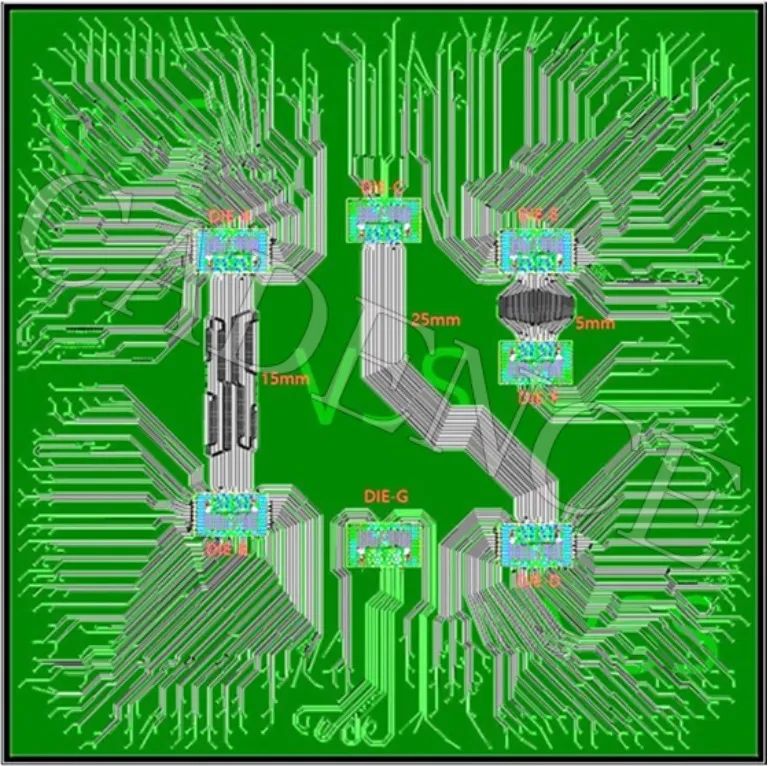

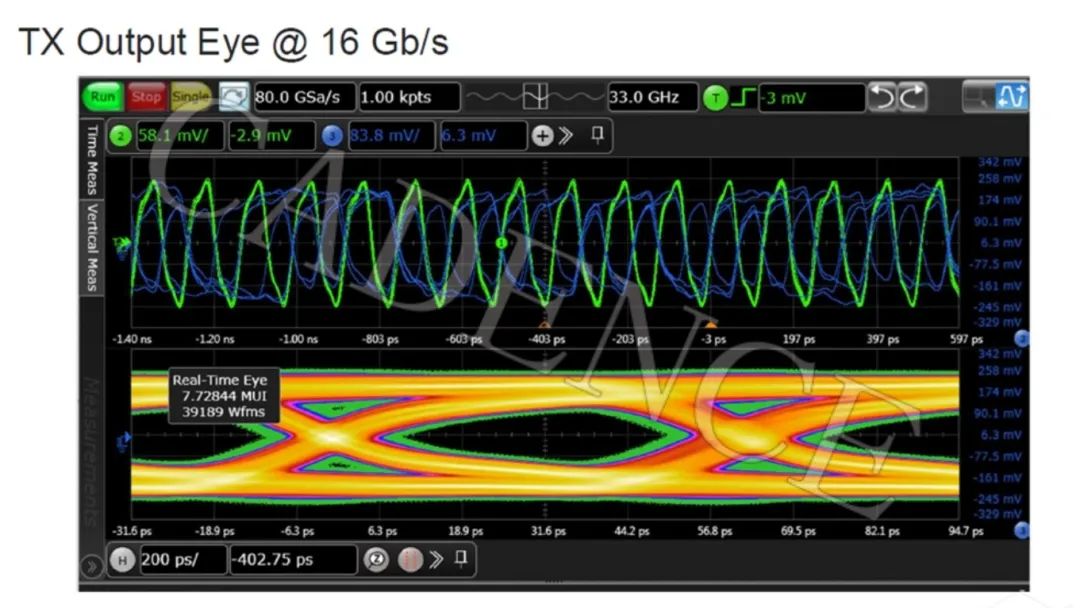

Cadence 在峰会期间推出了首款采用有机封装的 UCIe IP 芯片。这是业界首创,证明了在整个互连距离(短距离、中距离和长距离通道)上成功启动和数据传输,并以 16GT/s 的速度运行,且具有极宽的数据眼图。根据标准要求,所有互连距离都必须满足严格的 UCIe 要求。Cadence 是唯一一家在峰会上成功展示 5mm、15mm 和 25mm 长距离 UCIe 操作的 IP 提供商,以其全面的测量和报告树立了最高标准。

首次流片即成功的芯片具有不同距离的芯片间连接功能,使 Cadence 的设计人员能够收集有价值的信息,并向这些解决方案的最终用户展示我们的 IP 质量。该设计证明了我们对广泛测试和分析的承诺,而所有三个通道链路的开放数据眼图证明了 Cadence 拥有设计满足并超越规范的高性能 IP 的能力。

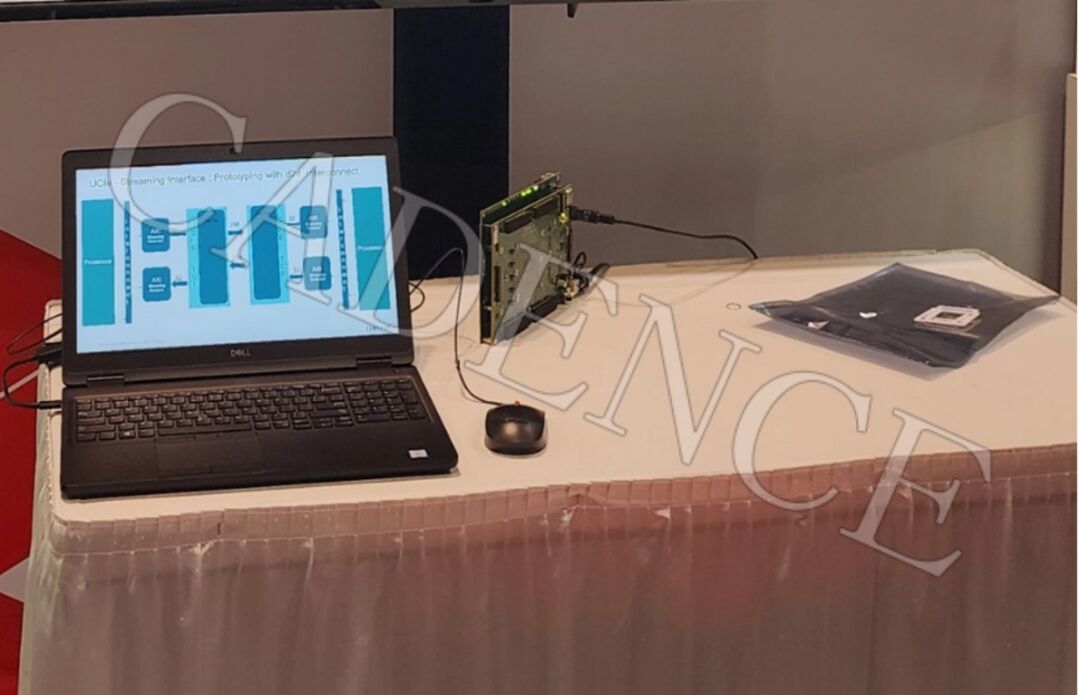

现场演示

测量显示出优异的特性。各操作频率(16GT/s、12GT/s、8GT/s 和 4GT/s)下的眼图都很清晰,并且链路训练和启动顺利进行。该启动包括完整的链路训练和自校准,无需任何手动覆盖校准循环或“调整”,展示了完全有能力的自训练 PHY。Cadence 演示界面的直观布局使访问者能够轻松理解数据并促进有意义的讨论。

硅样品显示了物理 PHY,而 FPGA 原型演示则显示了控制器和逻辑 PHY。使用 256 位并行接口,它可以构建 16 位 UCIe 接口原型,允许用户在接口两侧构建堆栈,甚至在 UCIe SerDes 和封装互连完成之前也是如此。此项联合开发能帮助客户缩短上市时间,并允许用户在设计周期的早期优化其系统以与 UCIe IP 一起使用。在演示中,原型经历了重置、链路训练状态机(LTSM),之后是任务模式流量,并可选择注入和观察错误。

关于 Cadence

Cadence 是电子系统设计领域的关键领导者,拥有超过 30 年的计算软件专业积累。基于公司的智能系统设计战略,Cadence 致力于提供软件、硬件和 IP 产品,助力电子设计概念成为现实。Cadence 的客户遍布全球,皆为最具创新能力的企业,他们向超大规模计算、5G 通讯、汽车、移动设备、航空、消费电子、工业和医疗等最具活力的应用市场交付从芯片、电路板到完整系统的卓越电子产品。Cadence 已连续十年名列美国财富杂志评选的 100 家最适合工作的公司。如需了解更多信息,请访问公司网站 www.cadence.com。

© 2024 Cadence Design Systems, Inc. 版权所有。在全球范围保留所有权利。Cadence、Cadence 徽标和 www.cadence.com/go/trademarks 中列出的其他 Cadence 标志均为 Cadence Design Systems, Inc. 的商标或注册商标。所有其他标识均为其各自所有者的资产。

京公网安备 11010802033920号

京公网安备 11010802033920号