革新ZVS软开关技术,Qorvo SiC FET解锁高效率应用潜能

从石器时代到信息时代,人类对高效率的追求从未停止。如今,随着人工智能、电动汽车和可再生能源系统等前沿科技的蓬勃发展,电力电子设备面临的挑战与日俱增。开关损耗一直是影响电力电子设备性能的关键因素之一,也成了人们对高效率追求路上的拦路虎。

面对这一挑战,尽管电力电子工程师们早就掌握了理论上能够达到零损耗的 ZVS 软开关这一秘密武器,但在纷繁复杂的实际应用中,由于寄生参数、控制精度、热效应、材料特性等种种因素,仍会不可避免地产生损耗。

在前不久 PowerUP Asia 2024论坛 的在线研讨会中, Qorvo 高级产品应用工程师Mike Zhu 分享了 Qorvo SiC FET在ZVS(零电压开关)软开关技术应用中的卓越表现 。

????点击视频,新知识一键get√

在传统的硬开关操作中,开关器件在高电压下导通,导致开关损耗显著,这不仅降低了效率,还产生了大量的热量。特别是在 高频操作 中, 开关损耗会急剧增加 ,成为制约系统效率和性能的关键因素。为了解决这一问题,软开关技术,尤其是 零电压开关技术 ,被开发出来,旨在 实现开关元件在无电压或极低电压状态下导通,从而极大程度地减少开关损耗,提高效率 。

零电压开关技术依赖于开关器件(如MOSFET或IGBT)的特性, 这些器件在导通时具有较低的电阻,而在关断时具有较高的电阻 。在ZVS应用中,开关在电压为零或接近零时导通,这意味着开关的电流在导通时不会突然增加,从而减少了开关损耗。

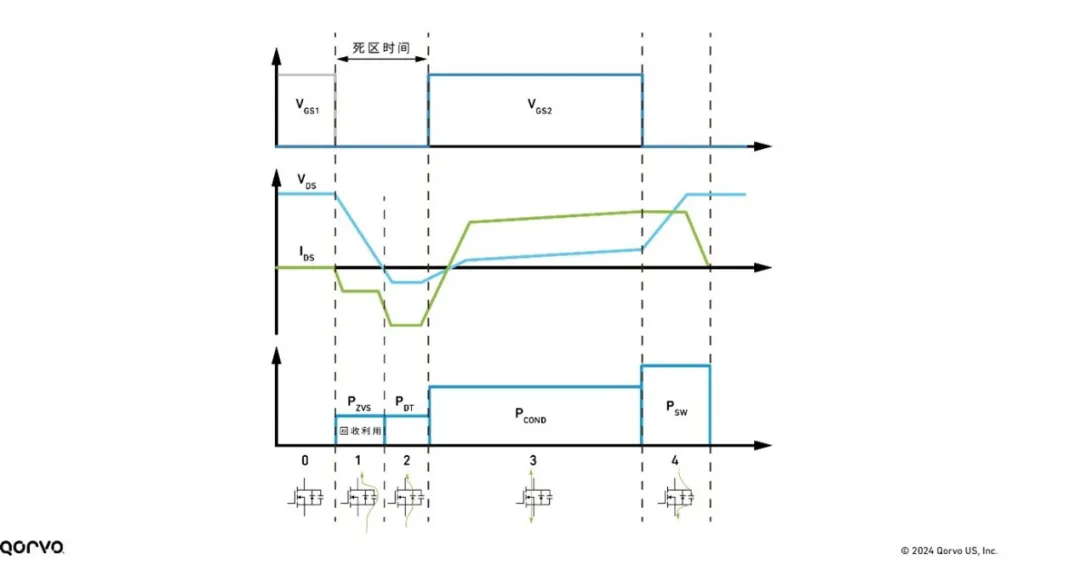

图1 ZVS软开关波形及不同开关阶段半桥电路的主要能量损耗来源

图1展示了一个ZVS技术的典型示例。根据其波形图我们可以看出, 尽管ZVS避免了开通损耗,但仍然存在死区时间 ,这一阶段会带来死区传导损耗。之后栅极导通,电流得以流过器件,ZVS应用中的主要损耗就发生在这里,这一部分就是 开通损耗 。当器件需要关断时,ZVS应用的关断方式依旧是硬开关式, 关断损耗 也就因此产生了。

在零电压开关应用中,功率器件的选择和设计需要特别考虑到几个关键性能指标,以确保系统在效率、热管理以及整体性能上达到最优。Mike 将其总结为以下几点:

-

低开通损耗 :在ZVS应用中,器件的开通损耗是首要关注的损耗问题,尤其是在第一或第三象限操作时。这要求器件在开通时能够迅速且高效地转移电流,同时最小化电压和电流的重叠,从而减少能量损耗。

-

低关断损耗 :尽管ZVS技术旨在降低开通损耗,但关断过程中的硬开关损耗依然存在,是第二大损耗来源。因此,器件在关断时应具备快速的电压转换能力和低损耗特性,以减少能量在关断过程中的消耗。

-

低栅极电荷(Qg) :ZVS应用由于消除了关断损耗,可以支持更高的开关频率。较低的栅极电荷意味着在高开关频率下,栅极驱动损耗更小,特别是在轻负载条件下,这有利于提高效率和系统稳定性。

-

低时间相关输出电容(Coss) :输出电容影响电压降至零的速度,进而影响死区时间。较低的输出电容可以缩短死区时间,提高占空比,从而向负载输送更高功率,同时有助于实现ZVS条件,减少开关损耗。

-

低热阻 :功率器件的热阻决定了其在高功率密度应用中散热的效率。低热阻可以有效降低器件的结温,提高器件的热稳定性和可靠性,从而延长产品的使用寿命。

Qorvo SiC FET,作为ZVS技术的革新者,凭借其独特的设计和材料科学的进步,为电力电子行业带来了前所未有的变革。

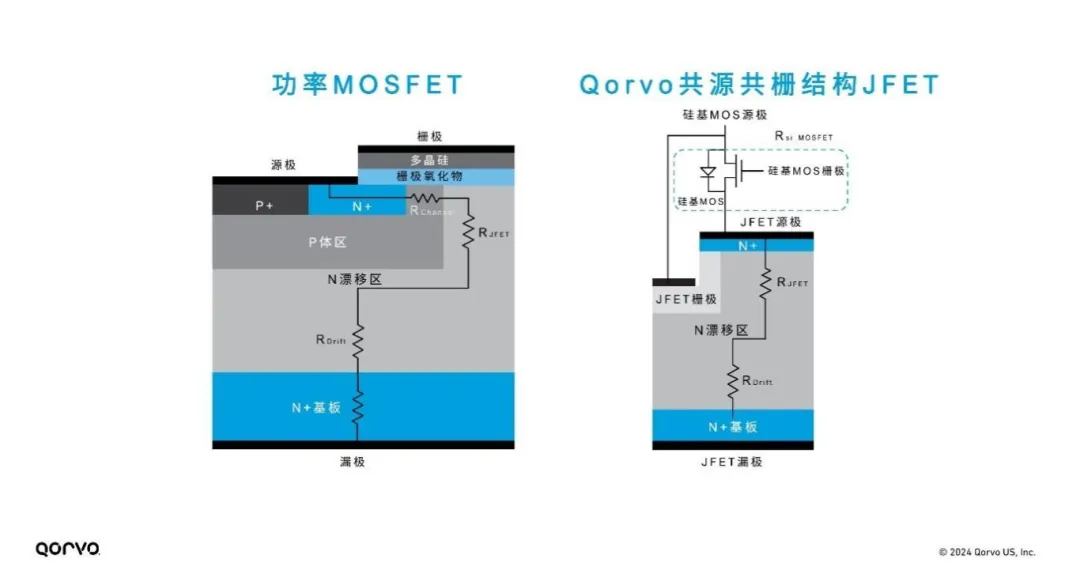

图2. SiC MOSFET与用于共源共栅电路SiC JFET的截面比较

与平面SiC MOSFET对比,Qorvo SiC FET采用了 共源共栅结构 , 其核心在于使用了沟槽JFET 。这一设计消除了平面SiC MOSFET中存在的沟道电阻,取而代之的是一个低压硅MOSFET的沟道电阻。由于硅材料的导电性能优于SiC,且工作在较低的电压下,因此其 导通电阻 显著减小, 仅占共源共栅器件总电阻的5%-10% 。这一创新设计大幅度降低了器件的导通电阻,使得 Qorvo SiC FET在单位面积上的导通电阻比最接近的SiC MOSFET结构低两倍以上 。

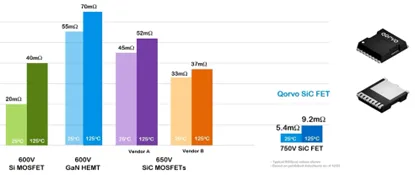

图3. Qorvo SiC FET与其他厂商的开关器件导通电阻对比

此外,Qorvo SiC FET还通过其独特的结构设计,进一步优化了开关性能。平面SiC MOSFET在第三象限导通时,体二极管压降较高,例如,在零偏置情况下传导30A电流时,压降约为4.8V。而在Qorvo SiC FET中,由于其共源共栅结构, 高压SiC JFET在第三象限导通时始终处于同步导通模式 。这使得在栅极偏置为0V且第三象限电流为30A时,Qorvo SiC FET的体二极管压降仅为2.5V。得益于其低沟道电阻和低体二极管压降, Qorvo SiC FET还提供了非常低的时间相关输出电容(Coss) ,这使得开关速度大大加快,并有效地缩短了所需的死区时间。

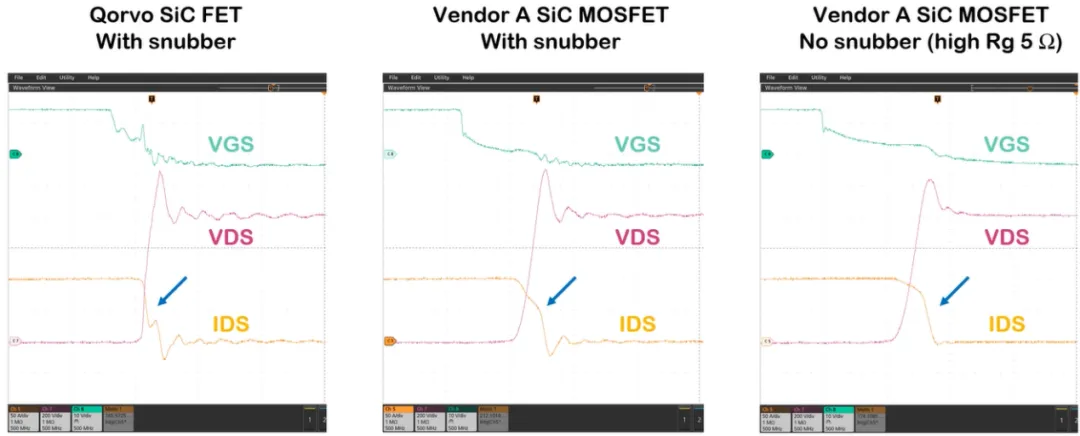

针对ZVS应用中的另一大损耗来源—— 开关损耗 。Mike将Qorvo的 U1B 半桥模块与其他厂商的SiC MOSFET进行了对比,结果显示在100A电流条件下, Qorvo的器件在关断时的开关损耗比其他厂商的器件低74% 。这种性能优势主要归因于Qorvo器件的更快的dV/dt,即电压变化率。

快速的dV/dt可以减少电流和电压的重叠 ,进而降低关断损耗。当使用缓冲器控制电压尖峰和振铃时,这种效果尤为明显。缓冲器可以帮助限制电压的上升速度,同时允许更小的栅极电阻,这有利于降低开关损耗。在电动汽车充电站等实际应用中,使用Qorvo器件可以实现 更高的效率 , 更低的结温 ,以及 可能更高的开关频率 ,从而减小系统尺寸和降低成本。

更小的芯片尺寸带来诸多优点的同时,也增加了热阻。在高功率密度的应用中,有效的散热设计至关重要。Qorvo通过采用 银烧结芯片贴装技术 ,显著提升了其SiC FET的热性能。 银烧结技术的导热率是传统焊接技术的六倍 ,这意味着热量能够更高效地从芯片表面转移到散热器,从而降低了器件的运行温度,延长了器件的使用寿命,并提升了整体系统的可靠性和效率。

Qorvo SiC FET的创新技术不仅在零电压开关(ZVS)应用中展现了卓越的性能,还为电力电子行业带来了显著的效率提升和成本降低。通过优化设计和材料科学的进步,Qorvo SiC FET在高频、高压操作中表现出色,满足了现代电力电子设备对高效率和高功率密度的需求。无论是在电动汽车、可再生能源系统,还是在工业电机驱动和数据中心电源等领域,Qorvo SiC FET都为实现更紧凑、更可靠的系统设计提供了无限可能。随着电气化和智能化的不断推进,Qorvo将继续引领技术创新,助力全球向更可持续的未来迈进。

京公网安备 11010802033920号

京公网安备 11010802033920号