[hpm_application] 超越jlinkV11, 先楫硬件SPI模拟SWD调试协议实现(二)

一、前言

在上一篇中 《 [hpm_application] 先楫硬件SPI模拟SWD调试协议实现(一) 》阐述了先楫的SPI外设模拟SWD的方案可行性验证,本文在上一篇的基础上,进一步验证方案性能。

本文对比的对象是segger的J-link plus compact V11。

调试器链接:

https://www.segger.com/products/debug-probes/j-link/models/j-link-plus/

该调试器的参数在segger官方有所描述,高速USB2.0(480Mbps),支持SWD/JTAG,最大接口速度为15Mhz。

而先楫HPM5301同样也具有480Mbps的高速USB2.0,SPI模拟SWD可达80Mhz, 本文就stm32f401作为测试平台,以jlink plus V11的最大频率15Mhz的clk作为对比,进一步再验证先楫45Mhz的swd效果性能。

二、性能对比

效果以逻辑分析仪抓取SWD信号计算每次的验证时间,比如擦除、烧录、校验所需的时间对比来进行验证。

另外以下的效果,hpm5301的执行代码都是放在外部flash。

逻辑分析仪的SWD信号文件会放在网盘中,有兴趣查看的可以私信本公众号。

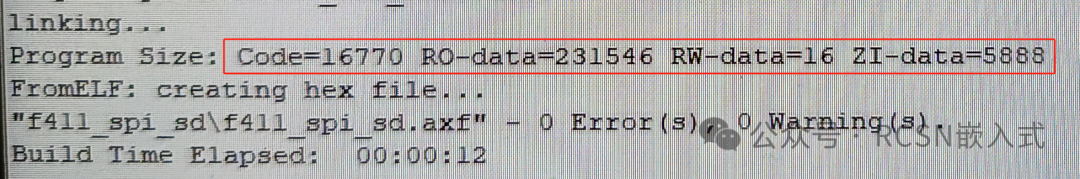

本文验证的目标芯片固件大小为240KB左右,如图

(一)纯SWD传输验证(排除目标芯片的flash影响)

纯传输验证就是固件只管进行SWD传输,不进行编程目标芯片flash(其实就是注释了flm算法工程里面所有对flash的操作,比如编程,擦除等),这就需要改动添加个flash的flm算法文件,这里的算法文件感谢@ Aladdin-Wang 开发者提供。如有需要可以在本公众号私信获取,后续会放在网盘。

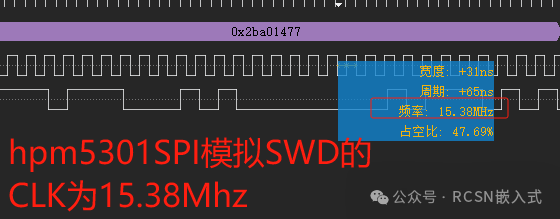

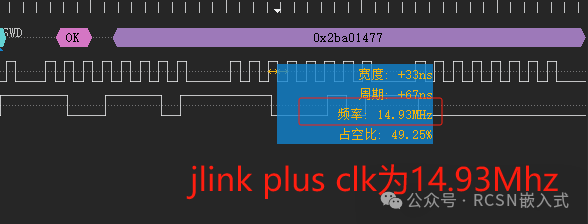

1、输出的SWD_CLK时钟大致都为15Mhz

2、program 240KB固件的传输时长有下可知,同样大概在15Mhz下,传输240KB,HPM5301模拟SWD需要1.37s, jlink的SWD需要1.86s。

在15Mhz下,hpm5301模拟的SWD性能比jlink plusV11快30%。

3、 在45Mhz下,传输240KB,hpm5301模拟的SWD传输时长只需要775ms。是jlink plus v11 15Mhz传输性能的2.4倍。

(二)实际目标芯片flash烧录性能

受限于目标芯片flash的擦除编程性能,特别是擦除性能,需要等待操作,擦除时间大致相同,校验也性能大致相同。

1、 在15Mhz下 ,对stm32f401进行全片擦除,也就256KB擦除时间,hpm5301模拟的SWD需要时间为4.49S,而jlink plus v11则需要4.81S, 在擦除时间缩短上,hpm5301相对jlink能提升10% 。

2、 在15Mhz下 ,对stm32f401进行编程240KB固件的时间,hpm5301模拟的SWD需要2.54S,jlinkV11需要4.23S, 在编程时间缩短上,hpm5301相对jlink能提升60%以上。

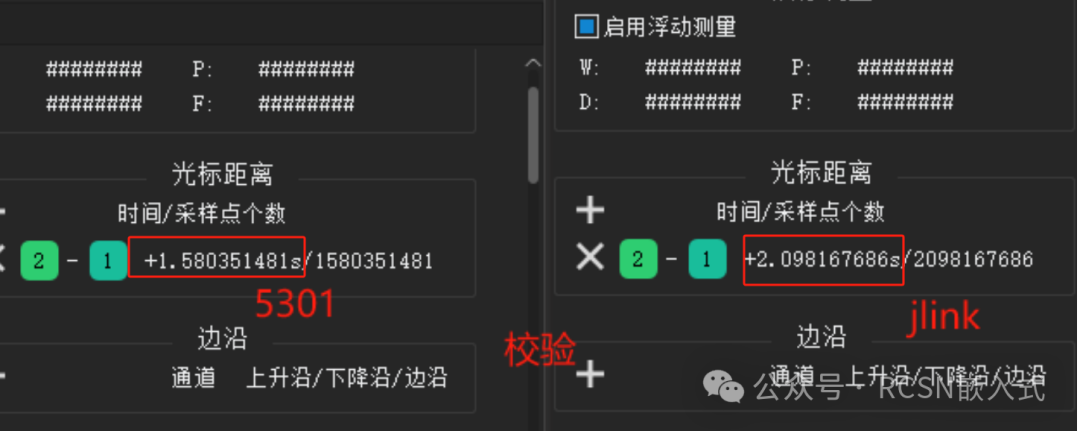

3、 在15Mhz下 ,对stm32f401进行校验240KB固件的时间,hpm5301模拟的SWD需要1.58S,jlinkV11需要2.09S, 在校验时间缩短上,hpm5301相对jlink能提升30%以上。

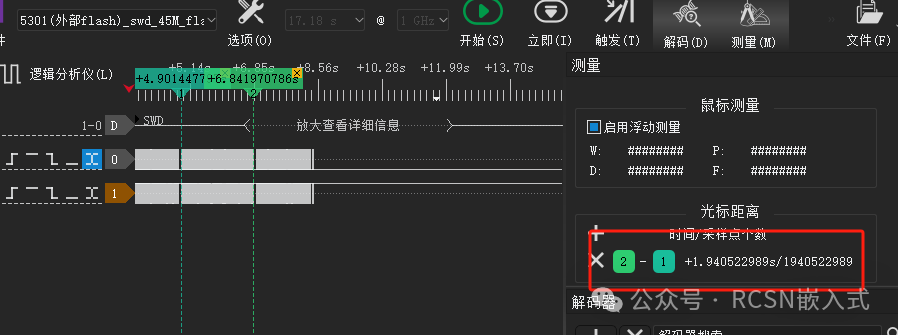

4、 在50Mhz下,对stm32f401进行编程240KB固件的时间,hpm5301模拟的SWD需要1.94S,相比15Mhz,时间缩短30%,这也于目标芯片的flash编程性能有关系,但整体能通过提高SWCLK频率来提高整体烧录调试性能。

三、CMSIS_DAP底层对接

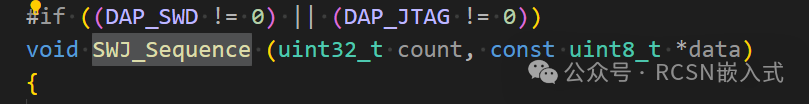

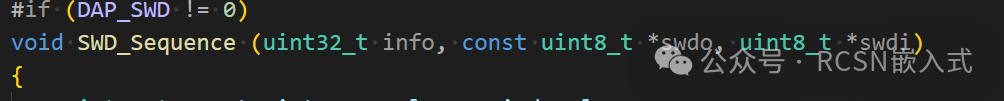

本文验证不涉及DAP协议处理优化,只针对传输底层进行优化,传输逻辑可参考上一篇文章。需要对接的API分别需要是:

1、SWJ_Sequence

2、SWD_Sequence

3、SWD_Transfer

四、相关分析

为何同样SWCLK频率下,hpm5301性能比jlink plus V11强大?

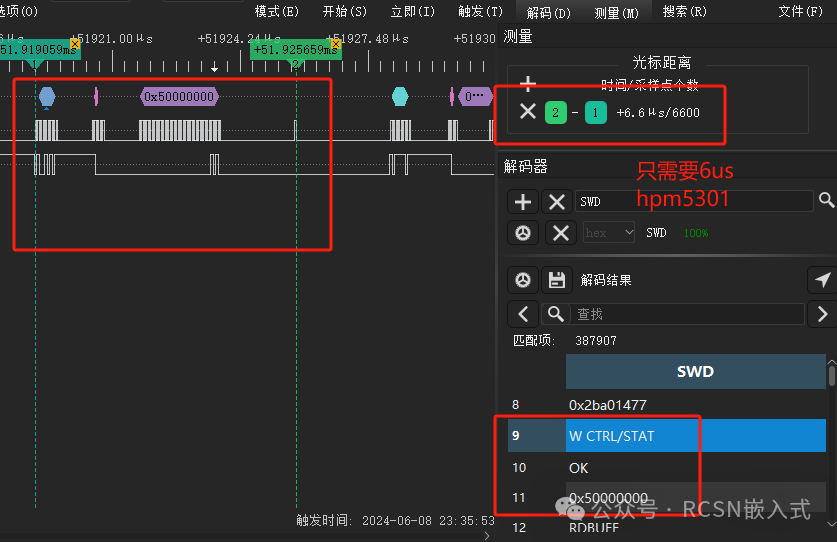

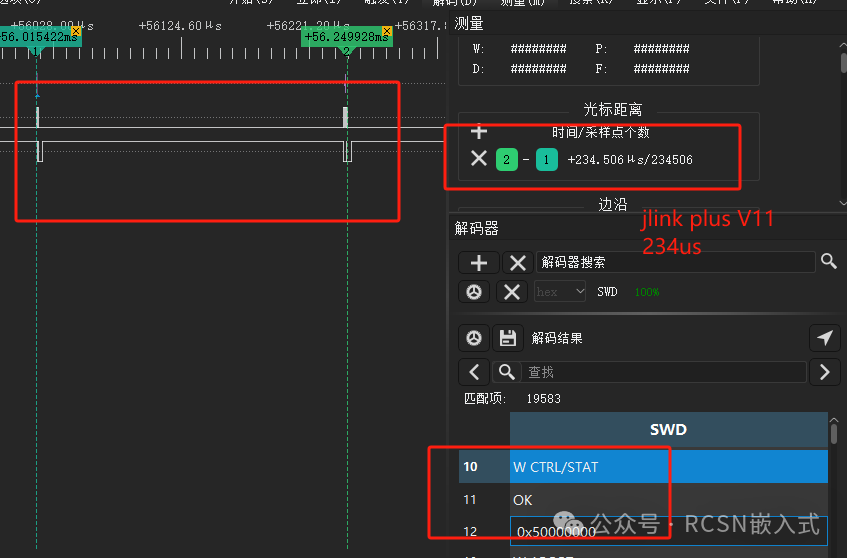

这里不涉及SWD协议处理逻辑上,jlink也有自己自定义的传输协议(这种专用的比通用的DAP传输效率更高),但从传输波形上看, 比如访问一次CTRL_STAT寄存器,hpm5301由于其强大灵活可变的SPI外设,这段访问只需要6us,相反jlink V11则需要234us。传输时间更大的弥补了协议传输的损耗。

五、总结

1、在实际测试中,SWCLK可以实现80MHz,但是找不到支持这么高频率的设备,欢迎大家测试上限。

2、同SWCLK频率下,烧录调试上,先楫模拟的SWD足够超过segger的jlink plus V11

3、得益于SPI的强大灵活性、16K I/Dcache、高性能高主频的MCU,制作高性能的调试器也不在话下。

六、展望

由于先楫hpm5300系列的usb支持16个双向硬件端点,实现daplink只消耗了5个硬件端点,还有很多的硬件端点空闲,可以继续实现usb转spi、i2c、can、pwm、gpio、多路daplink等功能,后续准备朝这个方向探索,挖掘hpm5300在做这方面应用上的上限,实现自己的all-in-one嵌入式开发利器。

京公网安备 11010802033920号

京公网安备 11010802033920号