超级高铁技术是一种十分新潮的交通概念,它有望以其高速、低压系统重新定义移动出行的未来。超级高铁的核心是在密封管网络中,乘客舱在磁悬浮和电力推进下,以超高速度行驶。确保如此复杂系统的无缝运行和安全性需要先进的控制和监控功能,而这正是FPGA的用武之地。

FPGA提供无与伦比的灵活性、安全性和高性能,可处理各类复杂任务,包括管理超级高铁网络中的推进、导航和通信等。凭借自身的可重新编程性、行业领先的安全功能和实时数据处理能力,FPGA在优化超级高铁运输系统的效率和可靠性方面发挥着关键作用,为更快、更安全、更可持续的旅行方式铺平了道路。

Swissloop原型车亮相2023年苏黎世公开活动

Swissloop是一个由苏黎世联邦理工学院赞助的学生组织,致力于研究超级高铁技术及其在现实世界中的应用,该组织多年来一直在使用莱迪思FPGA解决方案。该团队的全新原型机Bertrand Piccard采用了莱迪思FPGA解决方案,最近在苏格兰爱丁堡举行的第三届欧洲超级高铁周(EHW)上获得了五项大奖,包括完整的系统、电气以及传感和控制方面的奖项。

Bertrand Piccard是Swissloop的最新开发项目,具备了线性开关磁阻电机(LSRM)和电磁悬架(EMS)。LSRM将250 Kg的原型车以最大1.6 g加速度推进到60 km/h最高时速。推进系统由三个定制的逆变器单元提供动力,为推进系统提供720 V电压和6个高达120 A的矩形波电流。用于悬浮和横向稳定的EMS有自己的定制逆变器系统。这两个逆变器系统对控制提出了重大挑战。莱迪思MachXO3™ FPGA非常适合Swissloop的嵌入式应用,提供高能效和瞬时启动功能,成为平台“最先上电和最后断电”的器件,提供系统控制和电源管理功能,确保稳定、精确的悬浮。

舱体内部各种定制PCB

悬浮系统由八个电磁铁组成,每个磁铁都需要持续控制,以控制悬浮高度并确保与轨道的安全距离,避免碰撞。单个MachXO3 FPGA可以处理所有控制回路和数据采集,与悬浮系统并行工作,在推进系统中发挥着同样重要的作用。得益于二进制光门传感器,乘舱的位置可以精确到亚毫米级。随着速度的提高,乘舱和控制装置的定位难度也随之增加,莱迪思FPGA在推进系统中的预测控制功能可用于实现最高速度。

悬浮和推进组合系统凭借两片MachXO3 FPGA并行采集、过滤和处理数据,吞吐量高达1M Samples/s。在控件开发过程中,该团队大量使用了测试平台和仿真器,例如莱迪思版本的ModelSim。在发生错误时FPGA的快速响应以及用于EMC的信号同步使得FPGA比微控制器表现更佳。

此外,MachXO3 FPGA还提供了安全关键固件,这要求精确的时序控制,例如控制电池的继电器或电源开关的栅极信号。这帮助Swissloop团队在超级高铁舱上对安全关键系统实现了精确稳定的时序控制,也因此赢得了“感知与控制奖”。

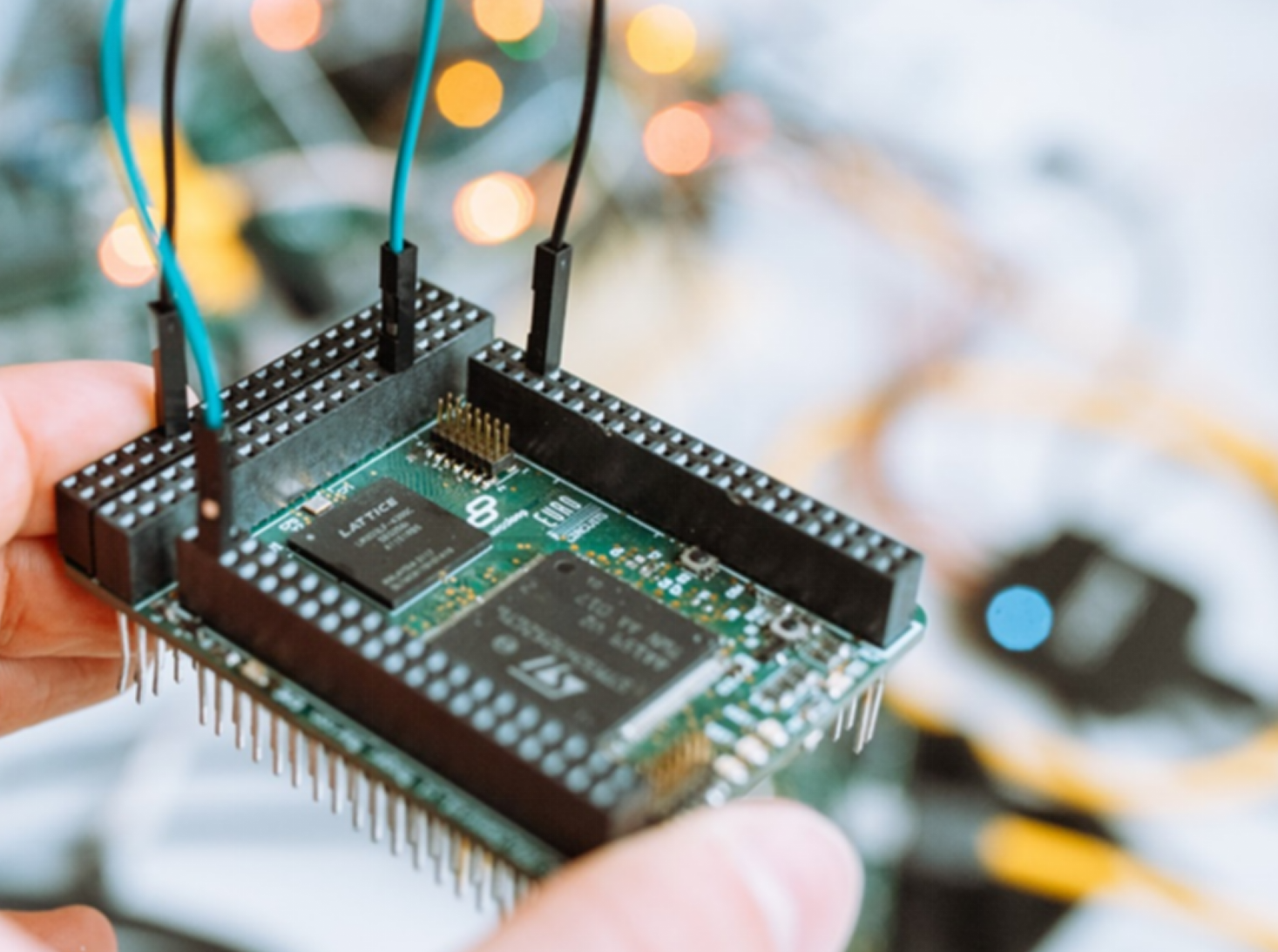

2023版MachXO3™通用控制板

对于Swissloop团队来说,2022/2023赛季以斩获五个奖项圆满结束,包括所有电气奖项。该团队将继续推动超级高铁技术的发展,他们对即将在苏黎世举行的第四届超级高铁比赛感到兴奋。该团队已经取得了重大进展,包括设计了新一代通用控制板,该板具有与FPGA连接的512 MB伪静态RAM,以太网功能以及用于编程和供电的USB Type-C控制器。

关键字:FPGA 高铁技术

引用地址:

FPGA助力高速未来

推荐阅读最新更新时间:2024-11-12 15:02

高云半导体发布最新的μSoC射频FPGA,可用手机蓝牙编程

中国广州,全球增长最快的可编程逻辑公司广东高云半导体科技股份有限公司(以下简称“高云半导体”)宣布发布其最新的μSoC射频FPGA,该产品集成蓝牙5.0低功耗无线电功能,可实现FPGA在边缘计算领域的全新应用浪潮。 边缘计算对可编程设备提出了新的要求。随着产品的差异化需求日益明显,高云半导体正在其下一代FPGA中集成各种新功能,其最新器件GW1NRF-4提供了4k LUT FPGA资源,集成32位低功耗ARC处理器和低功耗蓝牙(BlueToothBLE5.0),采用6x6mm QFN封装。此产品可以为传感器,音频,摄像机和显示接口提供灵活的IO,为并行计算和加速提供FPGA资源,并为控制,配置和电源管理提供微控制器,显著

[嵌入式]

以FPGA开发医疗IoT应用的优势

智慧医疗 整合个人生理状态感测与结合物联网,是众多IoT应用中的重点项目,因为 医疗 IoT应用市场的特殊性,不仅相关设备需达到高稳定性要求,同时所开发的产品受法规、产品验证严格管制,选择开发平台就成为左右成败的重要关键... 发展以IoT技术为基础的智能应用,选用平台是否适合应用投放市场的特性就相当重要,以智慧医疗的IoT物联网应用来说,由于 医疗设备 相较一般消费性电子、工业自动控制、智慧家庭等应用形是而言是相对严肃的应用场合,因为医疗设备稍有故障、误动作可能就会造成医疗失误,甚至危及用户健康与生命,不但设备相关的验证要求标准更高,针对应用需求设置的法规要求也相对严苛。 FPGA深入医疗电子设备开发应用

[医疗电子]

HDLC的DSP与FPGA实现

引言 HDLC(高级数据链路控制)广泛应用于数据通信领域,是确保数据信息可靠互通的重要技术。实施HDLC的一般方法通常是采用ASIC器件或软件编程等。 HDLC的ASIC芯片使用简易,功能针对性强,性能可靠,适合应用于特定用途的大批量产品中。但由于HDLC标准的文本较多,ASIC芯片出于专用性的目的难以通用于不同版本,缺乏应用灵活性。有的芯片公司还有自己的标准,对HDLC的CRC(循环冗余码校验)序列生成多项式等有不同的规定。专用于HDLC的ASIC芯片其片内数据存储器容量有限,通常只有不多字节的FIFO(先进先出存储器)可用。对于某些应用来说,当需要扩大数据缓存的容量时,只能对ASIC再外接存储器或其他电路,ASIC的简单易用性

[嵌入式]

基于FPGA的汽车ECU设计充分符合AUTOSAR和ISO 26262标准(二)

基于 FPGA 静态硬件的 ECU 设计 AUTOSAR 架构非常适合由 CPU、存储器和可编程逻辑组成的嵌入式系统。ECU 平台需要一个 CPU 或主机处理器来管理应用并处理分布在应用层的软件组件中的不同功能。同时,MCU 层和部分基础软件层可以在可编程逻辑结构中的硬件中综合。因此,除了能够实现与 CPU 相连的标准外设,其它定制外设和协处理器也能够在硬件中并存,并在软件中完全或部分地加以管理。 另外从功能安全的角度来看,专用协处理器或内核处理器也非常适用,因为用它们实现功能可让硬件从源头避免干扰,即便要求冗余性,也能给系统设计带来高灵活性。另外,居于中间的 RTE 层可以在分布于 FPGA 中的 RAM 模块中,或

[模拟电子]

英特尔推更简便FPGA 加快打入数据中心

当前的尖端科技如人工智能(AI)和机器学习(machine learning)需要处理能力强大、速度相当快的芯片,除了绘图处理器(GPU)之外,现场可编程闸阵列(FPGA)也相当符合要求,但需要复杂的专业技术辅助,英特尔(Intel)计划让FPGA变得更简便,让它们加速打入数据中心服务器应用。 FPGA可以随着不同的任务被重新改配置,长久以来被电信设备、工业系统、汽车、军事和航太产业所使用。但新式FPGA有大型的闸阵列、存储器区块,以及快速的I/O,适合更广泛的应用。 微软(Microsoft)服务器已经使用Altera的FPGA来支援Bing搜寻、Cortana语音辨识和自然语言翻译等许多服务背后的神经网路,Azure也

[半导体设计/制造]

Xilinx推出业界首款高性能DDR4内存解决方案

赛灵思交付业界首款数据速率高达每秒2400 Mb的All Programmable UltraScale器件内存解决方案。 2014年3月11日,北京 — All Programmable技术和器件的全球领先企业赛灵思公司 (NASDAQ: XLNX)今天宣布推出业界首款面向All Programmable UltraScale™器件的高性能DDR4内存解决方案,每秒数据速率高达2400 Mb。UltraScale器件采用ASIC级架构,可支持大量I/O和超大存储带宽,并能够大幅降低功耗和时延。赛灵思稳定可靠的内存解决方案可加速设计进程,并增加了对DDR4接口的支持。 UltraScale器件中的新增DDR4内存接

[半导体设计/制造]

采用高性能SRAM提高DSP密集型应用的性能

军事与国防应用极大地受益于数字信号处理器( DSP ),其广泛应用于雷达、软件无线电( SDR )、灵巧弹药与目标探测系统、电子战应用、飞机成像以及众多其它应用。 DSP 借助其完美架构提供的精确处理能力可以显著提高性能。关键 DSP 功能包括实时信号处理、超高吞吐量与可重编程功能。本文介绍了如何采用高性能四倍数据速率(QDR)SRAM而使整体DSP系统性能至少提高两倍(与使用 SDR AM的传统方法相比)的方法。 数字信号处理 数字信号处理包含把信号转换成数字形式后对其进行处理的方法,如:雷达处理。雷达系统基本上是产生可以通过定向天线馈送的脉冲。这些信号以光速传播,而其路径中的任何物体都会把

[嵌入式]

ARM-FPGA杜邦线之片间传输--高速数据串扰

片间传输--高速数据串扰 这几天调试一个东东,STM32的FSMC传输数据给Bingo自制的VGA控制器,由于没有直接打板,板间用了杜邦线连接。FMSC传输模式为最快的速度,FSMC写时序如下图所示,最快达到了72M(HCLK)的速度。但是我用了杜邦线,,没办法。。。神奇的事情不断地发生,幽灵一直在身边,以此分享给大家点滴心得,虽然我也只是知道皮毛。 下图是我项目中STM32与FPGA间,杜邦线连接的图,杜邦线20cm,FSMC 最高HCLK=72MHz。从右到左分别为D0-D15,CS,RS,WR,RD 先贴一下贵人相助时的聊天记录,众人经验总结,精华部分,值得分享:

[单片机]

FPGA中不可综合语句汇总

FPGA中不可综合语句汇总 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

AS6218-EK

AS6218-EK

京公网安备 11010802033920号

京公网安备 11010802033920号