ЁЁЁЁ

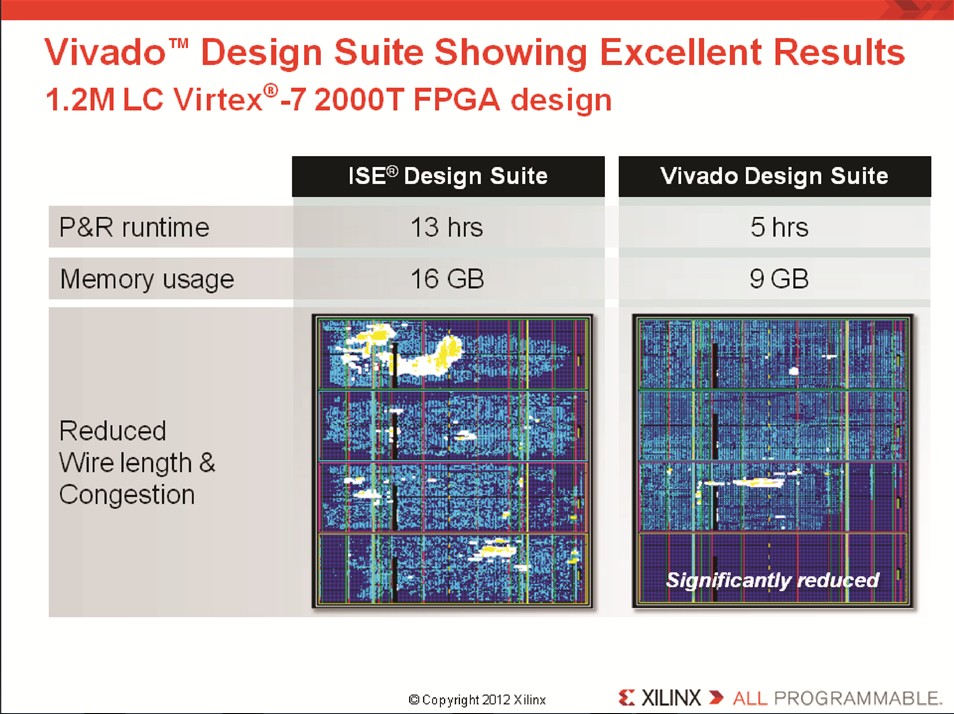

ШќСщЫМЯТвЛДњЛЗОГVivadoЭЦГі2012.2АцБОЃЌ ВЂЪзДЮУцЯђЙЋжкПЊЗХ. ЫљгаISE ЬзМўгааЇЦкФкЕФПЭЛЇОљПЩУтЗбЛёVivado 2012.2. ДЫДЮЗЂВМЕФзюаТАцБОАќРЈСНДѓжЕЕУЙизЂЕФжиЕуЃК

VivadoЦОНшвЛЯЕСаШЋаТвЛДњЯЕЭГЕНICЕФЙЄОпЮЊЩшМЦепЬсЙЉСЫвЛИіИпЖШМЏГЩЕФЩшМЦЛЗОГЃЌ ЦфжаАќРЈЃКИпВуДЮзлКЯЃЈвВОЭЪЧдРДЕФAutoESLЃЉЃЌвЕНчзюКУЕФSystemVerilogжЇГжЕФRTLзлКЯЃЌ ИяУќадЕФВМОжВМЯпЁЂЯШНјЕФЛљгкSDCЕФЪБађв§ЧцЕШЁЃ ЪЕЯжЫйЖШЬсЩ§дРДЕФЫФБЖЃЌ адФмЬсЩ§15%

ШќСщЫМзюаТЩшМЦЙЄОпVivadoЯТди

ШќСщЫМвЛШеЛђЖрШеХрбЕФкШн

ЗУЮЪШќСщЫМЙйЗНЭјеОСЫНтAll Programmable

|

ЁЁ ШќСщЫМAll Programmable SoC- Zynq 7000ЯЕСадйЖШЗЂСІ-ДІРэадФм Vivado ЩшМЦЬзМўМгЫйCгябдЪЕЯж ЫцзХVivado ЩшМЦЬзМўЭЈгУАцБОЕФЗЂВМЃЌШќСщЫМЛЙеыЖдAll Programmable 7ЯЕСа FPGAКЭZynq?-7000 EPP SoCЦїМўЭЦГіVivadoИпВуДЮзлКЯЃЈHLSЃЉЙЄОпЃЌМЬајбгајЦфдкЕчзгЯЕЭГМЖЃЈESLЃЉЩшМЦСьгђЕФСьЯШЕиЮЛЁЃVivado HLS НЋУтЗбЬсЙЉИјФПЧАБЃжЪЦкФкЕФ ISE ЩшМЦЬзМўDSPАцБОКЭЯЕЭГАцБОЕФгУЛЇЁЃЩшМЦШЫдБЭЈЙ§НЋCЁЂC++ЛђSystem CДњТызлКЯЕНRTLжаЃЌФмЙЛПьЫйЬНЫїГіИДдгЫуЗЈЕФЪЕЯжМмЙЙЁЃVivado HLSгыЯЕЭГЩњГЩЦїЃЈSystem GeneratorЃЉЭъУРМЏГЩдквЛЦ№ЃЌФмЙЛДДНЈГіПьЫйЗТецФЃаЭЃЌжЇГжЪгЦЕЁЂЭМЯёЁЂРзДяКЭЛљДјЮоЯпЕчЕШгІгУЕФПьЫйПЊЗЂЁЃVivado HLSВЛНіФмМгЫйЫуЗЈЪЕЯжЃЌЛЙФмНЋбщжЄЪБМфЫѕЖЬЖрДя1ЭђБЖЃЌВЂЭЈЙ§жЇГжRTLЮЂМмЙЙЬНЫїИФНјЯЕЭГадФмЁЃ |

|

ЁЁЁЁ ПьЫйМЏГЩЩшМЦЛЗОГИХвЊ ЛЖгVivadoЕФвЛИіПьЫйбнЪОЃЌЫќЪЧXilinxаТЕФЩшМЦЬзМўЃЌгІгУЕН7ЯЕСаКЭвдЩЯЕФЯЕСаЦїМўЁЃ ЕБФуДђПЊVivado

IDEМЏГЩЩшМЦЛЗОГЕФЪБКђЃЌФуЪзЯШПДЕНЕФЪЧПЊЪМвГЃЌдкгвБпЪЧЮФЕЕЃЌЗНЗЈжИЕМЪжВсКЭжИв§ЁЃ ДДНЈвЛИіаТЕФЙЄГЬКѓЃЌVivado IDEМЏГЩЩшМЦЛЗОГАќКЌЙЄГЬзмНсБъЧЉОЭДђПЊСЫЃЌетИіБъЧЉИјФугаЙиФуЕФЙЄГЬаХЯЂЃЌБШШчЯждкЕФзДЬЌЃЌБрвыСїГЬЃЌЩшжУЃЌДэЮѓКЭОЏИцаХЯЂЁЃ ЖЅВуВЫЕЅКЭЙЄОпЬѕИјФуЗУЮЪЕНЭЈгУЕФЙІФмЁЃ [ЯъЯИ] |

|

|

ЁЁ ЯъНтVivadoЩшМЦЬзМўДјРДЕФвцДІ ЁЁЁЁНтОіМЏГЩКЭЪЕЯжЕФЮЪЬт ЁЁЁЁЁАAll ProgrammableЁБЦїМўЃЌНЋЪЙЩшМЦЭХЖгВЛНіФмЙЛЮЊЫћУЧЕФЩшМЦБрГЬЖЈжЦТпМЃЌЖјЧввВПЩвдЛљгкARM?КЭШќСщЫМДІРэзгЯЕЭГЁЂЫуЗЈКЭI / OНјааБрГЬЁЃзмжЎЃЌетЪЧвЛИіШЋУцЕФЯЕЭГМЖЕФЦїМўЁЃSteve GlaserЫЕЁАЮДРДЁАAll ProgrammableЁБЦїМўвЊБШПЩБрГЬТпМЩшМЦИќЖрЁЃЫћУЧНЋЪЧПЩБрГЬЕФЯЕЭГМЏГЩЃЌЭЖШыЕФаОЦЌдНРДдНЩйЃЌЖјМЏГЩЕФЯЕЭГЙІФмШДдНРДдНЖрЁЃЁБ е§ЪЧЮЊСЫНтОіМЏГЩКЭЪЕЯжЕФЦПОБЃЌЪЙгУЛЇФмЙЛГфЗжРћгУетаЉЁАAll-ProgrammableЁБЦїМўЕФЯЕЭГМЏГЩФмСІЃЌШќСщЫМДђдьСЫШЋаТVivadoЩшМЦЬзМўЁЃ ...[ЯъЯИ] |

|

ЁЁЁЁЁЁЁЁ ИааЛФуЖдVivado HLSвВОЭЪЧXILINXЁЏs ИпВуДЮзлКЯНтОіЗНАИгааЫШЄЃЌетИіНтОіЗНАИзлКЯcЃЌc++КЭЯЕЭГcДњТыГЩVerilogКЭVHDL RTLНсЙЙЁЃ ЮвУЧвЊЫЕУїЛљгкcЩшМЦЗНЗЈдкЭМЯёДІРэЫуЗЈЪЕЯжЕФКУДІЁЃ етИіЫуЗЈЪЧЙЄзїдквЛеХВЪЩЋЭМЯёЃЌЭъГЩЩЋВЪБфЛЏКѓдйНјааБпдЕМьВтЁЃ

[ЯъЯИ] |

|

|

ЁЁЁЁIDE змЬхНщЩм ЕБДђПЊ Vivado ЙЄГЬКѓЃЌЛсгавЛИіЙЄГЬИХвЊЃЌЯђФњНщЩмЙЄГЬЕФЩшжУЁЂОЏИцКЭДэЮѓаХЯЂвдМАЙЄГЬЕФвЛАузДЬЌЁЃ дД дДЪгЭМгУгкЯдЪОЯюФПжаЕФЮФМўРраЭЃЌБШШчгВМўУшЪігябдЮФМўЁЂдМЪјЮФМўЁЂЗТецЮФМўКЭ IPЁЃФњПЩвдЪЙгУдДДњТыБрМЦїЃЌдкЙЄзїЙ§ГЬжаЬэМгЛђепДДНЈдДЮФМўЁЃ СїГЬЕМКН зѓБпЕФетИіВПЗжНазіСїГЬЕМКНЦї (Flow Navigator)ЃЌгУгкПижЦБрвыСїГЬКЭЗжЮіЪгЭМЁЃЫќЕФзщжЏЗНЪНгывЛАуЕФПЊЗЂСїГЬвЛбљЁЃЕуЛїфЏРРЦїЩЯЕФАДХЅПЩвджДааСїГЬЃЌвВПЩвдМгдиДІгкФГжжЬиЖЈзДЬЌЕФЩшМЦЃЌгУгкВщПДКЭЗжЮіЁЃ [ЯъЯИ] |

|

ЁЁШќСщЫМ VivadoЩшМЦЬзМўД№вЩ ЁЁЁЁVivado? ЩшМЦЬзМўЪЧЪВУДЃП ЮЊКЮвЊДђдьШЋаТЕФЙЄОпЬзМўЖјВЛЪЧЖд ISE ЩшМЦЬзМўНјааЩ§МЖЃП Vivado ЙЄОпФмНтОіЕБЧАЩшМЦШЫдБУцСйЕФФФаЉжївЊЬєеНЃП зюаТЛЗОГЯрЖдгк ISE ЩшМЦЬзМў14 ЩњВњСІЗНУцгаКЮгХЪЦЃП ШќСщЫМЪЧВЛЪЧВЛдйашвЊ ISE ЩшМЦЬзМўСЫЃП... |

|