编者按

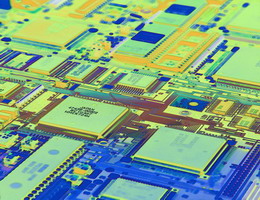

- 随着半导体工艺的飞速发展和芯片工作频率的提高,芯片的功耗迅速增加,而功耗增加又将导致芯片发热量的增大和可靠性的下降。

- 因此,功耗已经成为深亚微米集成电路设计中的一个重要考虑因素。 为了使产品更具竞争力,业界对芯片设计的要求已从单纯追求高性能、小面积转为对性能、面积、功耗的综合要求。

- DSP(数字处理器)作为数字系统的核心部件,其低功耗设计对降低整个系统的功耗具有重要的意义。 [详细]

低功耗DSP产品

- 各大厂商推出的低功耗系列DSP

- TI推出全新低功耗处理器发展策略开发人员现在首先要面对的问题是:我的设计在功耗方面有一定的限制,TI如何在这方面帮我更多?

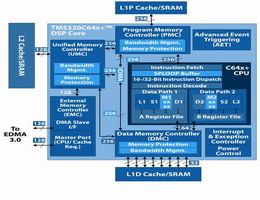

- ADI Blackfin™ 处理器架构概述在许多过去需要同时采用一个高性能信号处理器和一个单独的高效控制处理器的应用中,只需采用一个 Blackfin 处理器便足够了。

- TI SmartReflex™ 电源性能管理技术

- DSP核供应商灵活应对潜力应用

- ADI TigerSHARC™处理器的介绍

- LSI的数字信号处理器介绍

- CEVA推出高性能及低功耗DSP平台

- Octasic推出的异步DSP处理器

FPGA/MCU V.S. DSP

- 与DSP竞争的其他种类的低功耗产品

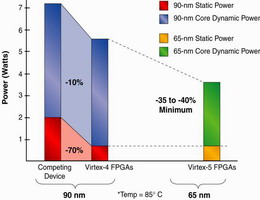

- 降低FPGA设计的功耗是协调平衡艺术目前许多终端市场对可编程逻辑器件设计的低功耗要求越来越苛刻。OEM希望采用FPGA的设计能够实现与ASIC相匹敌的低功耗。

- 各大厂商背水一战超低功耗MCU由于在三表、医疗、短距离无线联网、安防、家电等方面都具有诱人的前景,超低功耗MCU技术正在受到各大半导体厂商的关注。

- FPGA蚕食DSP与MCU市场

- MCU技术升级:高性能低功耗

- 低功耗FPGA设计技术

- FPGA厂商追求更低功耗和更低成本

低功耗DSP设计方法学

- DSP低功耗设计经典

- 如何处理好嵌入式DSP设计的功耗优化对基于数字信号处理器(DSP)的系统而言,优化功耗是一项重要但往往难以实现的设计目标。

- DSP系统的低功耗设计具体到任何一个实际的应用系统,在达到设计指标的前提下应对硬件、软件在多方面进行优化,尽可能地降低系统功耗。

- 一种降低DSP芯片总线功耗的设计方案

- 基于DSP低功耗多路数据处理系统设计

- 基于DSP低功耗接收机单边带解调方法

- 印度学生节省功耗的DSP设计技术

- 基于DSP的低功耗高速数据采集系统

- 嵌入式DSP设计中的功耗优化

- 定点DSP芯片实现快速算法

- 低功耗加密型语音硬件平台设计与实现

- 如何处理好嵌入式DSP设计的功耗优化

- 一种基于功耗管理的DSP处理器设计

低功耗DSP应用市场

- 新兴领域成为低功耗DSP的主力战场

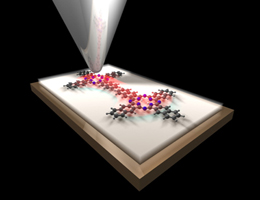

- 探寻DSP发展轨迹和未来趋势 无疑,CMOS工艺的改变大大降低了功耗,而且随着工艺节点不断提升至纳米级,低功耗是DSP一个不变的特性。

- 玩转DSP性能与功耗之间的零和游戏 “因为DSP牵扯到高速运算,所以功耗不会降到很低,”提及DSP的低功耗,一个工程师朋友小丁如是说。

- DSP 25周年:让梦想照进现实

- DSP正在朝节电方向发展

- 功率与性能:DSP设计面临的终极挑战

- 降低功耗:小心“过度设计”

热门专题

- 绝对关注

- 全球视野下的中国“芯”路 纯粹的纪念并没有意义。回首集成电路这50年来走过的道路,在全球视野下审视中国芯路,则令我们百感交集。

- 为了忘却的IC五十周年纪念

- 中国IC设计基地七“芯”之歌

- 凯明之殇,本土IC设计之痛

- 本土IC设计企业现状