简介

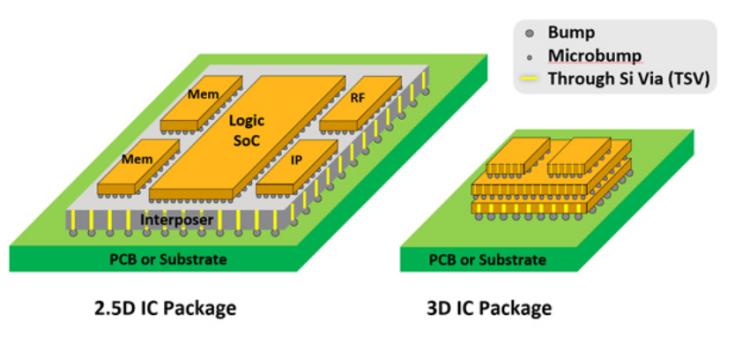

3D封装技术代表了一种创新的电子元器件封装方法,通过构建三维结构实现芯片、封装和基板之间的互联,以满足高性能、高可靠性、小型化、轻量化和低功耗等需求。

这种封装技术具有多项特点:提高了芯片密度和性能,减小了电路板的尺寸和重量,提高了系统的可靠性和稳定性,降低了系统的功耗和成本。

根据组装位置的不同,3D封装可分为垂直堆叠式和水平扩展式两种;按照封装工艺的不同,可分为TSV(Through Silicon Via)和W2W(Wafer-to-Wafer)等多种类型。

与传统的二维封装技术相比,3D封装技术具有诸多优势:充分利用了芯片面积和高度,互联线更短,信号传输速度更快;实现了异构集成,将不同功能的芯片封装在一起,降低了系统的功耗和成本;同时,还可以避免芯片接合面受错位、变形等影响,保持了更高的效率和性能水平。

相关讨论

推荐内容

Cadence Allegro 17.4零基础入门66讲PCB Layout设计实战视频

微电子技术导论

直播回放: Keysight 小探头,大学问,别让探头拖累你的测试结果!

控制系统仿真与CAD

MIT 6.622 Power Electronics

直播回放:基于英飞凌AIROC™ CYW20829低功耗蓝牙芯片的无线组网解决方案

直播回放:ADI & WT·世健MCU痛点问题探索季:MCU应用难题全力击破!

Soc Design Lab - NYCU 2023

动手学深度学习V2

直播回放: Allegro 下一代磁感应解决方案:XtremeSense™ TMR 技术如何促进高效应用

直播回放: Keysight 基于数字孪生的软件工具,助力射频子系统验证

PX4固件二次开发课程

PLC功能指令应用详解

RISC-V嵌入式系统开发

NuttX Workshop 2024

数字IC SoC HLS高阶合成 FPGA-快速入门与应用设计

Altium 3D封装库

Altium Designer常用器件3D封装

电容 AltiumDesigner 3D封装库

AltiumDesigner 3D封装库

Altium-常用3D封装库_Step_【接插件篇】

Altium-常用3D封装库(Step)【常用贴片篇】

Altium-常用3D封装库(Step)【常用贴片篇】 芯片.rar

Altium-常用3D封装库(Step)【常用贴片篇】 连接器.rar

Altium-常用3D封装库(Step)【常用贴片篇】 开关.rar

Altium-常用3D封装库(Step)【常用贴片篇】 晶振.rar

Altium-常用3D封装库(Step)【常用贴片篇】 发光器件.rar

Altium-常用3D封装库(Step)【常用贴片篇】 二极管.rar

Altium-常用3D封装库(Step)【常用贴片篇】 XTAL 11.2X4.7X3.6.rar

Altium-常用3D封装库(Step)【常用贴片篇】 TSSOP.rar

Altium-常用3D封装库(Step)【常用贴片篇】 TO-252-3.rar

Altium-常用3D封装库(Step)【常用贴片篇】 TO-126.rar

WiCAN:开源 ESP32-C3 CAN 适配器,支持 USB、Wi-Fi 和 BLE

基于esp32h2的开源微型赛车,灵感来源马里奥赛车

YOLO3D:基于yolo的3D物体检测在自动驾驶应用的项目源码

一个自动驾驶行业的工程师开源的功能超全的激光SLAM

BitNetMCU:在CH32V003 RISC-V MCU上,实现MNIST手写数字识别

超小型独立自主机器人Dimebots

OpenSimpleLidar:开源激光测距仪,可用于SLAM和导航

华为射频基础知识培训

丝网曝光定时器的制作

小小定时提醒器

电热毯温控器

温度范围监测系统

微型直流电机稳速电路

起重机用电阻器的安装与维修

NE555制作电器间歇工作控制器

NE555风扇周波调速电路