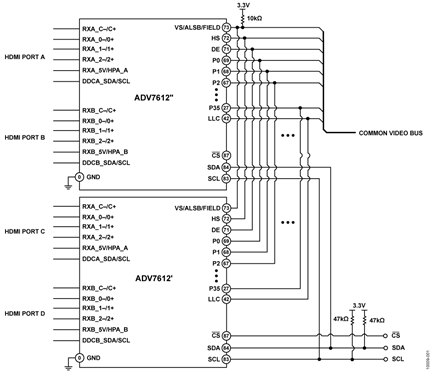

ADV7612 是一款双端口 Xpressview™ 225 MHz HDMI® 接收机,可在两个输入端之间实现快速开关。图1显示了使用两个ADV7612作为四路输入快速开关HDMI接收机的电路。

本电路显示了ADV7612的扩展性,在需要四个多路复用HDMI输入的应用中最高可达225 MHz TMDS(1080p60,每通道12位;148.5 MHz LLC像素时钟)或UXGA(1600 × 1200,每通道10位;162 MHz LLC像素时钟)。对此应用而言这是一种经济的解决方案,工作温度范围为−40°C至+85°C扩展工业温度范围。

ADV7612为双HDMI输入提供接收解决方案。图1显示如何在共享视频和音频总线上并联连接两个ADV7612,从而实现四个HDMI输入的多路复用。同时显示如何在不引起总线冲突的条件下设置I2C通信以及如何在信号源间切换。同时提供软件包,显示如何在HDMI中继器应用中处理通信和验证(参见 http://ez.analog.com/community/video)。

器件必须以非冲突方式从I2C总线加以控制。该电路的板布局十分关键,应遵循直线原理并使用可控阻抗,以降低反射和交叉耦合风险。完整PCB布局包括在设计支持包中,可从以下地址下载:www.analog.com/CN0224- DesignSupport。 ADV7511 HDMI发射机用作后端器件。

总线输出状态

复位后,ADV7612使引脚P0-P35、HS、VS/FIELD/ALSB、DE、LLC、AP0…AP5、SCLK/INT2和MCLK/INT2进入三态。这些引脚可通过寄存器TRI_PIX、TRI_SYNCS、TRI_LLC、TRI_AUDIO设置为有效状态,如UG-216硬件用户指南所述,请访问http://ez.analog.com/docs/DOC-1751

视频和音频总线载入

每次仅一个ADV7612可访问AV总线;第二器件必须保持三态。假设输出驱动器阻抗(P0…P35)为10 Ω至20 Ω(最高驱动强度)且走线特性阻抗为75 Ω,需要55 Ω至65 Ω的串联电阻以匹配走线的特性阻抗。ADV7612上的三态输出总线驱动器具有20 pF的最大电容(请参考ADV7612数据手册中的电气规格)。

布局和端接考量

对于本设计,必须确保传输线路得到正确端接且具有可控阻抗。否则,反射(可发生于较长线路上)可对发送的数据产生不利影响。

对于像素线路(P0…P35)、视频同步(VS/FIELD/ALSB、HS、DE)和音频线路(AP0、AP1/I2S_TDM、AP2...AP5、MCLK/INT2、SCLK/INT2)——LLC除外,建议在ADV7612驱动器端使用51 Ω的串联端接电阻,以及特性阻抗为75 Ω的走线。

线路锁定时钟(LLC)线路具有相同的75 Ω特性阻抗,不应有串联电阻,但远端应采用对称端接(150 Ω至+3.3 V以及150 Ω至GND),如图2所示。 虽然理论上最佳端接值介于50 Ω与60 Ω间,但测试中发现对称75 Ω (2 ×150 Ω)端接可增加摆幅,使信号以中间电源(1.65 V)为中心,这一点十分理想。ADV7511 HDMI发射机包括在电路板上,用于发送两个ADV7612的多路复用输出。

图3至图6显示各种端接的波形。每种情况下,对称LLC端接被放置在远端(靠近ADV7511),串联端接电阻尽可能靠近两个ADV7612器件,如图2所示。

使用Tektronix P6243 FET探头(1 MΩ阻抗,1 GHz带宽,电容小于1 pF)和Tektronix TDS5104B示波器在ADV7511引脚上执行测量。

从波形可看出,在LLC线路上使用2 × 150 Ω端接确保了3.3 V的最大摆幅。

在数据线路上使用75 Ω会使边沿速度过低。数据线路上的33 Ω和15 Ω导致下降沿欠冲(图5和图6)和上升沿过冲(未显示)。因此LLC选择了2 × 150 Ω,数据线路上使用51 Ω,图9和图10中的眼图做了说明。

I2C 访问

上电后,两个ADV7612器件在主映射上将具有相同I2C 地址,这可能导致冲突。

两个器件上均提供一个CS CS 引脚,允许选择两个器件之一。CS线路拉低后, I2C 通信启用。

CS 线路拉高后,I2C 通信禁用。

CEC

电路板上是否实施CEC取决于最终用户,而非强制性。如果不需要CEC,CEC引脚应保持浮空(如 UG-216,的附录B:未使用引脚的推荐配置所述)。此用户指南可从 http://ez.analog.com/docs/DOC-1751下载。

另一种情况下,应使用独立引擎处理CEC命令。

XTAL_N、 XTAL_P

驱动ADV7612时钟有两种方式。两个器件可具有连接到XTAL_N和XTAL_P引脚的独立晶振,或者可共享相同信号时钟。本电路中,振荡器发出的的1.8 V信号时钟被提供给两个器件的引脚XTAL_P。在此配置下,XTAL_N必须保持浮空。必须确保正确的布线和接地布局,以消除敏感线路间的耦合。总线每条走线的长度应相同。

中断

两个器件的中断必须予以考虑。ADV7612具有两种可能的中断:INT1(INT1引脚)和INT2(通过SCLK/INT2、MCLK/INT2或HPA_A/INT2提供)。

不建议通过引脚MCLK/INT2或SCLK/INT2使用INT2,通过TRI_AUDIO寄存器使音频总线进入三态也会使这些引脚进入三态。

布局考量

布局应由极短走线组成。理想情况下,在两个ADV7612间连接相同功能的两个引脚的走线应可能短,并应共享同一串联端接电阻,该端接电阻尽可能靠近两个器件,然后连接到总线。实际上,由于布局限制此要求不可能满足;因此每个器件需要自身的串联端接电阻(参见图2)。视频走线应尽可能接近相同长度,以提供延迟匹配。

评估与测试

评估本电路时,利用两个视频发生器(Quantum Data 882)生成UXGA 1600 × 1200像素、30位和1080p60、36位视频(Samsung2和MoirèX图案)。使用Astro VA-1831视频分析仪作为HDMI接收器(从ADV7511输出)。此外,将P6243(1 pF,1 MΩ,1 GHz)探头连接到Tektronix TDS5104B示波器,然后在ADV7511引脚上观察ADV7612的视频信号(LLC和P35)。所得波形用ADV7511眼罩表示为眼图,图9和图10显示了Samsung2图案的UXGA视频(162 MHz、30位)。测试期间使用的MoirèX图案还显示了类似的安全裕量。

通过Astro VA-1831测量视频时序,未显示异常。分析MoirèX的偶数和奇数垂直线路(1080p60 36位和UXGA 30位),显示所有位同时正确切换,线路间无任何泄漏(MoirèX图案)。Astro VA-183还显示,稳定的HDMI同步信号和数据包具有正确的CRC校验和。这说明后端ADV7511正确接收了时钟和同步信息。

测试步骤

解决方案框图

!注意:请使用浏览器自带下载,迅雷等下载软件可能无法下载到有效资源。

| 器件 | 类型 | 描述 | 数据手册 |

|---|---|---|---|

| ADV7511 | HDMI/DVI 变送器 | 集成ARC的225 MHz高性能HDMI®发送器 | 点击下载 |

| ADV7612 | HDMI/DVI 接收器 | 双端口XPRESSVIEW 225 MHZ HDMI接收机 | 点击下载 |

欢迎加入EEWorld参考设计群,也许能碰到搞同一个设计的小伙伴,群聊设计经验和难点。 入群方式:微信搜索“helloeeworld”或者扫描二维码,备注:参考设计,即可被拉入群。 另外,如您在下载此设计遇到问题,也可以微信添加“helloeeworld”及时沟通。

EEWorld Datasheet 技术支持